Last Modified; September 24 2000

![]() パスコン

パスコン

![]() 3端子レギュレーター

3端子レギュレーター

![]() フィルター

フィルター

![]() オペアンプ

オペアンプ

![]() アイソレーション

アイソレーション

![]() 時定数

時定数

![]() リミッター

リミッター

|

CRによる時定数はよく使用される。CとRの組み合わせにより、微分、積分の回路となる。 カットオフの周波数の範囲では(微分では以下、積分では以上)動作的には数学の微積分そのものの動作となる。 その充放電の時定数はt=CRであらわされる。また周波数的には3dB落ちのカットオフ周波数は1/(2*π*CR)で表される。 この時入出力のインピーダンス(抵抗)を考慮に入れなければならない。 この時定数の基本回路は一般に入出力とグランド間にCRを入れた回路で表される。 またそうでなければならないと思っている人がいるが、別にグランドでなくても電源(グランドと等価)であってもよい。 電源のインピーダンスが低く、CRの時定数が電源に負担にならなければいいのである。 動作的には充電と放電が入れ替わるが、時定数としては同じである。 また場合によりグランドではなく電源の方が動作的には都合のいい場合がある。 例えば充電される電圧が+電圧から−電圧に変化する場合、電解コンデンサは+側の高い電圧からの時定数とすれば、極性に問題はなくなる。 トランシーバーなどでは送信と受信が切り替わり、送信時のみ動作する回路、受信時のみ動作する回路がある。 たとえばAGC、スケルチ、ノイズブランカの時定数は受信時、ALCは送信時、その他のミュートである。これらが送受信で切り替わるとき、 その動作において立ち上がりを考慮したとき、最初から充電しておいて欲しい(ある程度電圧が必要)回路、 あるいはすぐ放電して欲しい回路(早く立ち下がって欲しい)がある。この時グランドとの間での時定数を組んでいた場合はどうなるか。 たとえば受信用の電圧が立ち上がってから、の電圧により回路の動作が始まり、 それでCに充電するなどといった場合はその時定数により立ち上がりがかなり遅れてしまう。 立下りも放電するまでの間しばらく電圧が残っている。例として、切り替わり時にノイズを出したり、頭切れしたりするのである。 こんな時はCをグランドではなく送受信用の電源との間に接続して時定数とする。 こうすればCの+側は受信電源電圧で動作するから、この間との充放電となり切り替わり時にいきなり高い電圧側からスタートし、 やがて充電されて電圧が下がってくる。終了時はこの充電された電圧分だけいきなり受信電圧と同時に下がる。 このために立ち上がり、立下りが非常に速くなる場合がある。 過渡的な現象を考慮し、同期させて動作させてやればいいのである。 |

|

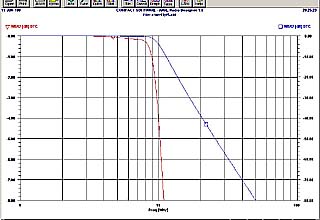

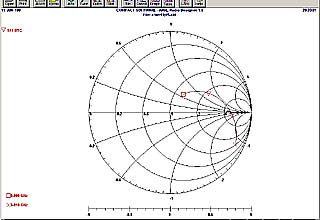

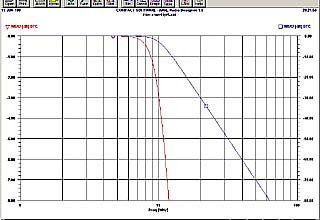

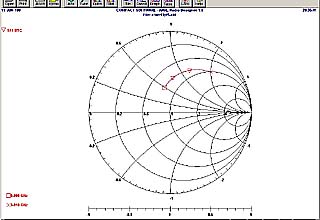

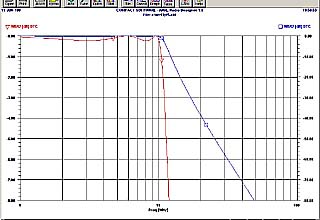

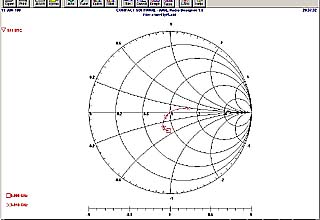

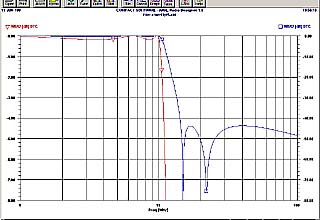

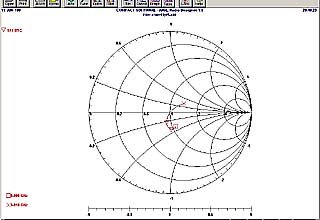

フィルターの項でバターワースの不利な事を説明した。実際にどの程度なのか実例で検証してみよう。 ちょっと図が小さくなって見えにくいと思うが勘弁してほしい。

実際に各形式にて10MHzの5次LPF(または3次の2段)を設計し、それをあるシミュレーターにかけてみたのが下記の図である。

バターワースのみ10MHzで-3dB、他は-0.2dB(SWR1.5程度)で設計してある。 1番上は通常アマチュアの設計でよく見られる、3次のバターワース(C−L−Cのπ型)を2段重ねたもの エリピティックが非常に切れのいいことがよくわかるであろう。

この減衰極を2倍、3倍の高調波に当たるように微調すれば減衰量の少なさがある程度カバーできると思う。 バターワース5次とチェビシェフは少しだけチェビシェフが良いぐらいであろうか。 しかし肩特性を見るとチェビシェフが10MHzまで使えるのに対して、バターワースの方は7-8MHzぐらいの帯域のフィルターとしてしか使えない。 3次の2段は徐々に落ちているのが見える。 バターワースの設計周波数を下げて使用する周波数を通過特性に合わせると、グラフから2倍の高調波はチェビシェフ約38dB バターワース3次x2が約25dB バターワース5次は約20dB程度にしかならない。 さらに帯域内のSWR特性をみればどれがいいかは歴然である。しかもこの3者では使用している素子の数(L2個、C3個)は変わらないのである。 チェビシェフやエリピティックは設計リップル量を大きく取ると傾斜も急になるが、素子そのものの影響を受けやすいため、少な目に設計することがこつである。 とはいえ帯域の周波数特性、および帯域内のインピーダンス特性はバターワースに比べると圧倒的に有利なので、 群遅延などが問題にならない高周波出力のフィルターなどはチェビシェフやエリピティックフィルターがよく使われる。 時折りバターワースなどを変形し、Lに並列にCを入れて極周波数を意図的に作った、エリピティックもどきのFILTERを見かけることがある。

しかしこれらのFILTER特性はきちんと設計されたものに比べて、周波数特性、帯域内特性ともに到底及ばない。

さらにリップルが大きくなったり、減衰域の山がそろわなかったりしている。

連立チェビシェフ特性がきちんと設計され、再現されているかどうかは、これらリップルと減衰域の特性を見るとある程度わかる。

|

|

|

Butterworth 3次 10MHzで設計した3次フィルターを2段重ね |

|

|

Butterworth 5次 10MHzで-3dB |

|

|

Chebyshev 5次 リップル 0.2dB |

|

|

Ellipitic 5次 リップル 0.2dB |

|

|

インピーダンス変換は、例えば増幅回路の入出力のインピーダンス変換など、高周波回路のいろいろの場面で用いられている。 同調コイルのLとCが決まれば、Cを2つに分割し直列接続とする。この2つの直列Cによる合成容量が元の同調容量である。

さらに変換したいインピーダンス比でこの2つのCの比を決定する。 この方法を使うと比較的楽に変換ができる。 さらに例えば2つの同調コイル間を小容量のCで結合する複同調回路などでは、容量が実現できないほど小さくなったり、 小さいために誤差が大きくなり、自由な値が選べない。 こんな時は上記の方法を使ってそれぞれの2個のグランド側を共通Cとして結合すれば実現しやすくなり、 この共通C(比較的大容量)を調整して結合度を決めることができる。 固定LやCのフィルターの回路などにおいても、インピーダンスによってはLやCの値が使用する周波数において実用的でなかったりする。 BPFの様にLCの同調回路が含まれていれば、Cタップの方法で自由に変換し(昇圧、降圧)実現しやすいLやCの値を使ったりすることができるのである。 ただしこの方法はLタップと比較すると直流的にはカットされるため、使用場所によっては不利なこともある。しかし逆に直流カットが利点になることもある。

|

|

最近は結構大出力のAFパワーアンプのICが安価に手に入る。このICを使う上での注意点について。 これらのICの出力はOTLとなっており、直流カットのコンデンサを通して直接に負荷のスピーカーが接続される。 ICの出力インピーダンスは非常に低いから、低周波最大出力電力は負荷となるスピーカー、および電源電圧でほぼ決定されてしまう。 P=E^2/R = 4^2 /8 =2 (W) である 5VのICであれば約0.35Wである。実際にはいわゆる無歪み最大出力(10%歪み)は少し増えて約2.2-2.4Wぐらいであろうか。 出力を上げるには少し電圧を上げることと、負荷インピーダンスを下げればよい。4Ω負荷であれば出力は約2倍、2Ω負荷では4倍になる。 (どこまで負荷インピーダンスを下げられるかはICの能力による) 良く定格出力が出てこないという事で問題になることがある。しかしこの場合使用する側の問題であることが結構多い。

というのは負荷インピーダンスが非常に低いため、ジャックなどの接触抵抗や、スピーカーまでの線の抵抗などで思った以上に測定値を落とすことがある。

使用する側もそんなに簡単に影響するとは思っていないので細い線を使ったりする。 出力に入れるコンデンサは8Ω負荷だと470uF(カットオフは約40Hz)程度、 4Ωだと2倍の容量が必要になる。 この容量が少ないとサグ(sag)が出てきて、低域のDC成分に影響が出てくる。もう一つ、4Ωの負荷というのは非常に低いインピーダンスであるから、 使用するコンデンサもできれば低インピーダンスの物を選ぶ。 出力端子には高域の発振を抑えるためのCRがよく使用される。 さらに出力からスピーカまでの線はリターンのグランド側を含めて、専用にパターンや線で引くぐらいの配慮が必要である。 これが守られてない場合には出力波形に微少な発振が見られる場合がある。 これらのICはゲインも非常に高く、IC自身の雑音出力は入力インピーダンスでほぼ決まってしまう。

常に出力に雑音が伴う場合は問題は出ないが、送信時や、スケルチなどの無音状態、さらに受信信号の雑音抑圧状態時には、

値にして数mV以下ではあるがこのICの内部雑音が結構大きく聞こえてくる。

これを下げるには入力インピーダンスをできるだけ下げることである。

AFパワーアンプの入力側には音量調整のVRが接続されてることが多いが、これを絞ったときには低インピーダンスになるために雑音も下がるために有効である。 12Vなどの電源電圧を直接使用しているために、電源変動により雑音が出ることがある。

例えばSSB送信機などは送信時に音声に応じて電源電流が大きく変動している。

このための電圧降下により電源電圧が大きく変動し、この変動がAF

ICの電源を通して出力に出てくる。またこのICの電源に入っている大容量の電解コン(パスコン)自体に蓄えられている電荷の移動が問題になることがある。

この対策のためには大きな容量のLや、TRによるリップルフィルターなどを電源ラインにデカップリングとして挿入することになる。

|

|

測定器などで使う精度の良いものもあるが、精度はそんなに必要としないがゲインの調整や、

回路間の緩衝などの目的のために回路上のいろいろなところで使用される。 形としてはπ型、T型があるがどちらも効果、動作は同じである。(周波数特性的には各エレメントに有利な抵抗値があるから違ってくる)、またL型が使用されることがある。

この場合はアンテナのインピーダンスにより減衰量が変化するのであるが、リレーの1回路のみでスルーとの切り替えができるため、簡単なところで良く用いられる。 オートマチックアンテナチューナーなどでは、ATTを通過するように回路を切り替え、送信機に対して整合動作中のSWRを下げて動作の安定化をはかっている物もある。 ひとつだけ面白い使い方を紹介しよう。送信機とアンテナの間、アンテナ直下に送信機のパワーに耐えられる3dB程度のATTを入れる。 こうするとアンテナがどれだけインピーダンスが変化しようとSWR=3に収まる。

最近のTRを使った無調整の送信機は、だいたいSWR=3以上では保護回路を動作させてパワーを大きく抑えてある。 そのままつなぐとSWRの高いアンテナではほとんどパワーが出ないが、この緩衝作用によりSWRを抑えると一応パワーは出るし、送信機も安泰である。

あとは出力側の整合条件で空中に放出される電力が決まることになる。当然アンテナのSWRが低い方が効率はいいわけであるが、 たとえどんなにSWRが悪くてもなにがしかのパワーが空中に出る。とにかく送信機からまずパワーを絞り出すことである。

この方法は意外と使える。敷地がなくてショートワイヤしか張れなくても簡単にオールバンド対応となる。 非常に非効率なわけで、嘘だと思われる方がいるかも知れないが、これに近い物が実際に実用されて市販されているものもある。 |

|

トランシーバーでは送受信の切り替えSWやPTT(Push To Talk)スイッチが必要である。送信時のみ動作する回路、受信時のみに動作する回路、常時動作が必要な回路がある。またダイオードSWなどで送受切り替え用の電圧が必要なために、受信回路用、送信回路用のそれぞれ安定化電源を作りそれらを一つのPTTSWなどで切り替える。しかし電源をOFFしても回路中の電解コンデンサなどにチャージされている電荷は残っている。OFFにされた回路自身が負荷になっていずれ放電されるが、切り替えた直後に急速に放電した後、ダイオードの接合電圧以下になると回路の動作自身が負荷にならなくなるために、そこから後は放電時間が極端に長くなる。早い切り替え時間が必要な場合、回路中の電解コンデンサをできるだけ小さくしたりする。大きなコンデンサが必要な回路で動作に問題がなければ、送受信には関係なく常時動作させる。また早く放電させるために意図的に放電用の抵抗(普段は無駄な抵抗?)を入れたり、OFF時に放電するための電源ショートSW回路を入れたりする場合がある。 雑誌などで発表されている回路を見ていると、2つの回路を一つの接点にてON/OFFしているものが見受けられる。例えばPNPのオープンコレクタと、NPNオープンエミッタの回路を用いベースを共通として、極性の違いからどちらかがON、もう片方はOFFになっているといった回路である。これらの電圧が同時に出ないように立ち上がりに時定数を持たして遅らせたりする。 PTT SWが理想的に完全なスイッチとして動作している時には問題はない。PNP/NPNのベース電圧は0Vとの間で瞬時に切り替わるからそれぞれの電源回路も瞬時に切り替わる。(コンデンサの電荷による放電時間の問題はある) このような不安定な接点に対しては、ただ一つのON/OFFのスイッチ回路を用い、その出力結果で上記の様な複数の切り替え回路を動作させるのである。このスイッチ回路もじわじわ型の物では問題が出るために、デジタルICや、コンパレータなどのスレッショルド電圧から急激に出力が反転する(ゲインが高い)回路を用いる事である。つまり複数回路の切り替えの前でON/OFFを完全に決定づけることである。またチャタリングの対策用に接点に時定数回路を用いる。 上記のような問題が出ないかどうか確かめる方法として、PTTの端子にVRを接続して高い抵抗値から徐々に低い抵抗値で落としてみると良い。切り替わるはずの両電圧が同時に出たりする場合は大問題である。徐々に落とし、ある抵抗値で瞬時に切り替わったり、どちらも動作しない領域が有る場合はOKである。どの程度の電圧/流出電流で切り替わるか確かめておくと良い。トランジスタSWなどをPTTに接続した場合にはその残留電圧やSINK電流値が問題になる場合が有るからである。また極端に接点電流が少ない場合はちょっとした漏れ電流で切り替わってしまうし、高周波が回り込みやすいから問題が出やすい。 |